Definition

An Interrupt is an event that requests the attention of the processor

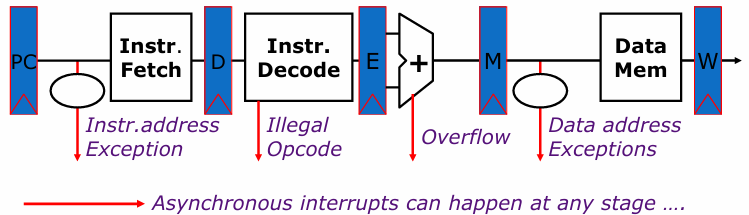

We can classify interrupts into two categories: asynchronous and synchronous.

-

An asynchronous interrupt occurs independently of the execution flow and does not depend on the current instruction being processed. These are typically external events such as an I/O device request, timer expiration, or issues like power failures or hardware malfunctions. Asynchronous events are often easier to manage because they can be handled after the current instruction completes, making their timing predictable.

-

A synchronous interrupt is caused by the execution of a specific instruction. These events happen as a direct result of the processor’s actions, such as an undefined opcode, an integer overflow, a floating-point unit (FPU) exception, misaligned memory access, or virtual memory exceptions (e.g., page faults, TLB misses, and protection violations). These types of events are more complex to manage because they arise within the instruction execution and must be handled before the instruction can be completed, making their behavior less predictable.

Interrupts can also be classified based on the level of control they offer.

- User-requested exceptions are those triggered by predictable external events like I/O operations. These are handled after the current instruction has completed, and they rely on the same mechanisms used to save and restore the state of the system.

- Coerced exceptions, which result from hardware failures or other external disruptions not under the control of the user program, are typically more difficult to manage due to their unpredictable nature.

Another important distinction in handling exceptions is whether the exception is maskable or non-maskable.

- A maskable exception can be disabled by the user program, essentially allowing the system to control whether it responds to the exception.

- A non-maskable exception, however, cannot be disabled and must be addressed immediately, regardless of the program’s state or intent.

This distinction is particularly relevant in systems where certain hardware errors (such as power failures) need to be handled immediately to prevent further damage or data corruption.

When an exception is triggered, the program’s execution may either resume or terminate. If the event is considered a resume event, the system can continue the execution of the program after the exception has been handled. However, if it is a terminate event, the program is stopped, often due to the irrecoverable nature of the exception (e.g., a critical hardware failure or illegal operation).

There is also a distinction between precise and imprecise exceptions. A precise exception is one where the state of the system is well-defined, allowing for the program to resume execution at the exact point of interruption. This is typically the case when the processor’s state can be fully restored to a consistent condition. In contrast, an imprecise exception is one where the system’s state is ambiguous or inconsistent, requiring the program to terminate, as it is no longer possible to guarantee that the execution will proceed correctly.

Asynchronous Interrupts

Definition

An asynchronous interrupt occurs when an external event demands the processor’s attention, usually from an I/O device or hardware malfunction. When such an interrupt occurs, the processor invokes the interrupt handler, which is a specialized routine designed to handle the event. The interrupt handler is typically part of the operating system and operates in kernel mode, where it has higher privileges than regular user-mode applications.

The process begins when an I/O device requests attention by asserting one of its prioritized interrupt request lines. Upon detecting this signal, the processor suspends its current execution and stops the program at the instruction

Once the PC has been saved, the processor disables further interrupts and transfers control to the interrupt handler, ensuring that the interrupt is addressed without interruption. This is important because nested interrupts, where multiple interrupts may occur in rapid succession, require careful handling to ensure that the system does not get overwhelmed.

For nested interrupts, the system must save the PC before allowing any additional interrupts to be processed. This involves using General Purpose Registers (GPRs) to store the PC, as well as masking further interrupts until the current state is safely stored. Additionally, the processor reads a status register to determine the cause of the interrupt. After processing the interrupt, the system uses a special instruction, RFE (Return From Exception), to restore the PC, re-enable interrupts, and return to user mode. This instruction also restores the processor’s hardware status and control state, allowing execution to resume from where it left off. The instruction

Synchronous Interrupts

A synchronous interrupt, also known as an exception, is triggered by an issue arising during the execution of a specific instruction. Unlike asynchronous interrupts, synchronous interrupts are internal events that occur due to the processor’s direct actions during the execution of an instruction.

When a synchronous interrupt occurs, the instruction causing the exception,

In a pipelined processor, where multiple instruction stages may be processed in parallel, handling synchronous interrupts becomes more complicated. If an interrupt occurs, the processor must undo the effects of one or more partially executed instructions in the pipeline, ensuring that no incorrect results propagate through the system. This action requires specific mechanisms to ensure the integrity of the processor’s state is maintained and that the execution flow can return to a consistent point after handling the exception.

Exception Handling in a 5-Stage Pipeline

In a 5-stage pipeline, exceptions can arise during different stages of instruction execution. These stages typically include IF (Instruction Fetch), ID (Instruction Decode), EX (Execution), MEM (Memory Access), and WB (Writeback). Due to the concurrent nature of pipelined execution, exceptions can occur out of order, meaning that one exception might be detected in an earlier stage while another is detected later. This can lead to complications in determining the correct order for handling these exceptions.

Example

For instance, suppose a data page fault is detected during the MEM stage of the first instruction, while an arithmetic exception (such as a division by zero) is detected during the EX stage of the second instruction. These exceptions might be raised simultaneously in a pipelined processor. However, the page fault must be handled before the arithmetic exception, as it pertains to memory access, which must be resolved before continuing execution.

Out-of-Order Exception Handling Problems

To resolve the challenge of handling exceptions that arise out-of-order, several strategies can be implemented:

-

Hold Exception Flags Until the Commit Point: One approach is to hold the exception flags within the pipeline and defer reacting to the exception until the instruction reaches the commit point, which is the end of the MEM stage. This strategy ensures that the processor does not immediately interrupt the instruction flow but instead handles exceptions in the correct order as they reach the commit stage.

-

Pass the PC Through the Pipeline: Another solution is to pass the Program Counter (PC) through the pipeline. By saving the PC at the point where the exception occurs, it can be restored after the exception handler has completed. This approach effectively postpones the exception handling until the MEM stage, allowing the processor to behave similarly to an unpipelined processor by processing exceptions in the order in which they occur.

-

Raise Exceptions at the MEM Stage: A third approach is to wait until the instruction reaches the MEM stage before raising the exception. This ensures that all earlier pipeline stages are completed before any exception handling is triggered.

Exception Handling Process at the Commit Point

Once an exception is raised and the instruction reaches the commit point (just before entering the WB stage), the following steps occur:

Steps

Save the Program Counter (PC): The processor saves the PC into a special register called the Exception Program Counter (EPC). This is important because the processor needs to know where to resume execution after handling the exception.

Store the Interrupt Handler Address: The PC is then updated to point to the address of the interrupt handler routine. This allows the system to transfer control to the appropriate handler to address the exception.

Convert Subsequent Instructions into NOPs: The instructions that are currently in the pipeline, especially those in earlier stages (such as IF and ID), are turned into NOPs. This effectively stalls these instructions, preventing them from being executed until the exception is resolved.

Handle Interrupts in the IF Stage: The processor then handles the interrupt using a “faulting NOP” in the IF stage, ensuring that no further instructions are fetched or executed until the exception has been processed.

Resuming Execution After Exception Handling

After the exception handler routine has completed, the following steps occur to resume normal program execution:

-

Re-execute the Faulting Instruction: The instruction that triggered the exception is re-executed. This is important because the system has now resolved the issue (e.g., a page fault or overflow) and can safely continue processing that instruction.

-

Continue Instruction Flow: Following the re-execution of the faulting instruction, the instruction flow proceeds as normal, with the processor fetching and executing subsequent instructions.

Throughout the exception handling process, exception flags and the PC are held within the pipeline until the instruction reaches the commit point. This ensures that exceptions in earlier stages of the pipeline take precedence over exceptions in later stages, and that external interrupts are injected at the commit point, overriding any other exceptions that may have occurred.